Our technologies

DIS Tech uses advanced design technology to get you to your perfect design with shorter lead times.

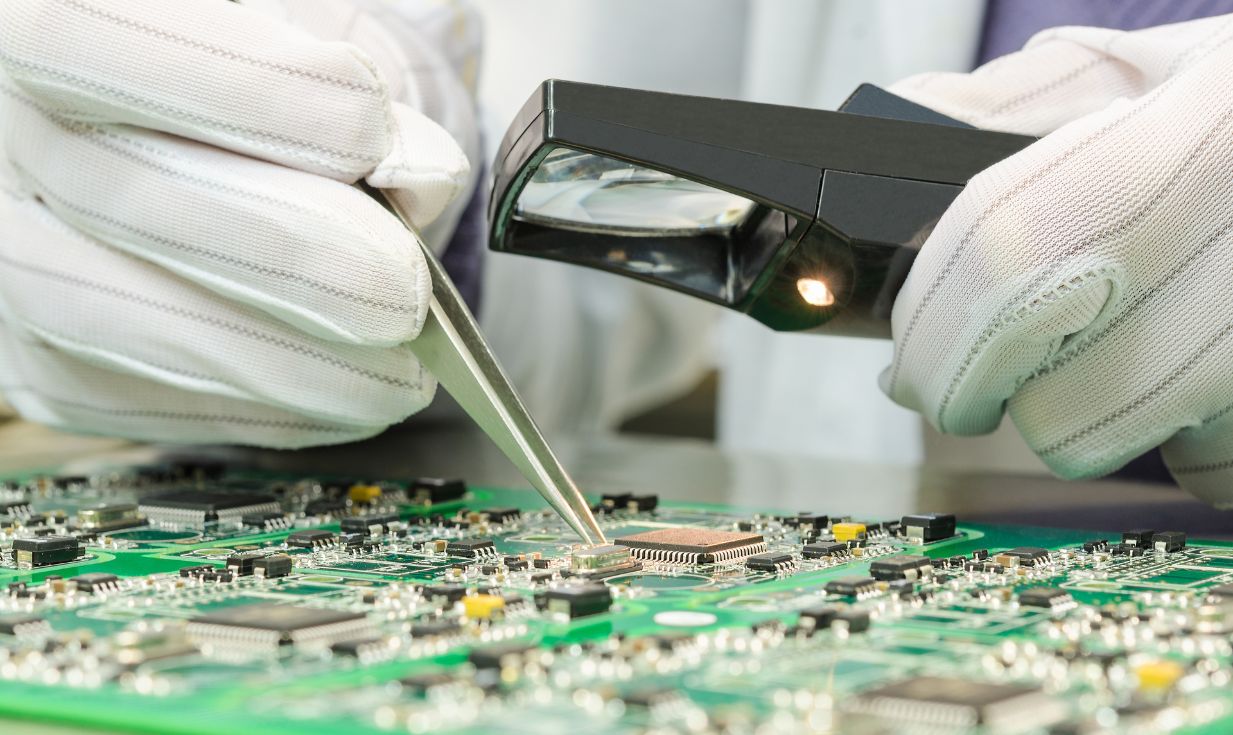

We offer advanced System in Package (SiP) design tool integration, automated full-board simulation capabilities, and extensive CAD tool automation for enhanced design and fabrication validation. Through these unique advances, combined with close co-development of manufacturing techniques and design rules with our supply chain partners, DIS Tech ensures first pass board yields of greater than 90%.

DIS Tech is striving continuously to enable the highest site count possible final test and wafer probe applications to maximize your tester efficiency. Currently, DIS Tech has the capability to design and fabricate interface boards with device pin pitch down to 60µm. With DIS Tech as your partner for device interface hardware, we’re confident your production floor will be running with the highest efficiency possible.

What about test and diagnostics for new hardware designs?

That’s our specialty. On-Tester DIB-Diagnostics are possible for every new interface board, providing high fault coverage with or without a shorted-socket/wafer contact point. An extension of these diagnostic tools that integrate with the production flow provide the ability to continuously monitor the ‘health’ of a device interface board enabling early detection and diagnosis of damaged or defective components and avoidance of production test running on un-characterized hardware performance – risking poor yields or test escapes impacting downstream performance and quality.

MLO space-transformer technology

DIS Tech is experienced in designing, simulating, and integrating Multi-Layer Organic (MLO) space-transformer technology which enables translation of the tester signals to the fine pitch requirements of the device pins. Implementation of this unique technology enables high site count wafer probe cards with good Touch Down Efficiency (TDE).

Interface Hardware Complexity

Complex devices have unique pin density, speed, power and thermal requirements to consider. DIS Tech recognizes increasing Device Under Test (DUT) sites and pin count drive up the pin area density which requires routing the I/O and power to the DUT with an increasing mechanical load. Complex devices require connections to high performance I/O such as high-speed digital, wireless and high voltage which can create a signal integrity issue when combined with very tight pin and DUT spacing and high DUT count.

Systems Development Lifecycle

The systems development approach includes: interface design, interface manufacturing, performance verification, diagnostics/QC, maintenance and service, and production operations support. The goal of this approach is a fully integrated design and manufacturing solution. Rigorous specification and quality management avoids the costly mistake of passing along defects. Complete with integrated certification, repair, maintenance, calibration and Bin-1 validation.

An integrated design and manufacturing system is able to scale effectively as complexity increases.

Total Cost of Ownership

The four main phases of a semiconductor development lifecycle, from a test perspective, include: interface engineering, test engineering, ramp engineering and production engineering.

Monitoring all of these key performance indicators enhances performance, quality and on-time delivery which delivers lower cost of ownership.